Authors

Rick Hearn, Senior Product Manager, Curtiss-Wright Defense Solutions

Mike Slonosky, Senior Product Manager, Curtiss-Wright Defense Solutions

Geoffrey Waters, Senior Systems Engineer, NXP Semiconductors

Lisa Sarazin, Marketing Portfolio Manager, Curtiss-Wright Defense Solutions

In recent years, ARM processors have made a quiet, understated entry into the aerospace and defense market. With a well-established reputation in commercial markets for bringing high performance to low-power mobile devices, such as smartphones, tablets, and wearables, it’s no surprise that ARM’s potential was recognized in an industry where size, weight, and power (SWaP) constraints heavily influence technology selection.

ARM, once an acronym for Advanced RISC Machine, employs reduced instruction set computing (RISC) to decrease cycles per instruction, which in turn lowers the processor’s power consumption and dissipates less heat. Consequently, ARM architectures deliver an unparalleled power-to-performance ratio to meet the requirements for many aerospace and defense applications.

Even so, ARM chips are far from ubiquitous in the mil-aero industry, a world that has been long dominated by Intel and Power Architecture processing units. These incumbents offer rugged processors that are optimized for maximum performance, have been implemented in boards with a minimal physical footprint, and have been proven to maintain reliability in harsh environments. What’s more, because Intel and Power Architecture processors have powered many avionics systems to date, a variety of these chips provide the service history and design artifacts required for DO-254 certification.

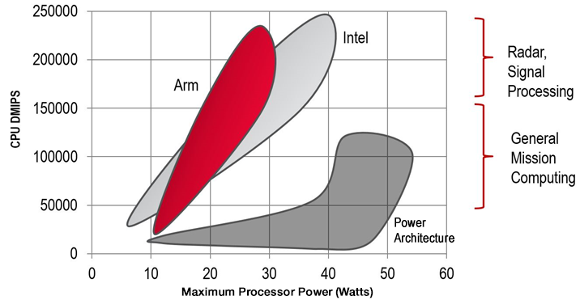

Figure 1: Processor architecture performance and power consumption comparison1

A previous white paper explored in depth why ARM processors are ideal for aerospace, defense, and rugged embedded applications. But, with a SWaP-friendly nature and proven history in commercial technology (ARM Limited reports 50 billion chips were shipped from 2013 to 20172), do ARM processors have what it takes to meet the highest DO-254 requirements?

Filling the Power Architecture void

The company ARM, unlike Intel, does not make or sell ARM processors, but owns the architecture intellectual property and licenses it to manufacturers such as NXP Semiconductors, NVIDIA, Apple3, Qualcomm, and Samsung. Similarly, the term “Power Architecture” describes a processor architecture as opposed to a brand of product. Power Architecture processors have been most commonly produced by NXP (formerly Freescale) and IBM.

Power Architecture processors also use RISC to provide low-power computing, and those manufactured by NXP have been proven in a wide range of DO-254 safety-certifiable applications, both commercial aerospace and defense, often to the highest design assurance level (DAL). But with no NXP Power Architecture devices planned for introduction after the currently released QorIQ T-series of products, this landscape is set to change in the future.

In particular, the absence of new Power Architecture offerings creates an opportunity for both ARM and Intel, especially in programs with DO-254 requirements. The selection process for embedded computing technology in these safety-certifiable programs has typically prioritized reliability and determinism, which made Power Architecture processors’ non-throttling performance an ideal fit. Now, with computing technology evolving at a more rapid pace than in the past, performance has become another key criterion.

The challengers

Historically, Intel processors have touted the highest performance levels for rugged, embedded computing applications. Single-board computers (SBCs) and digital signal processors (DSPs) equipped with Intel chips have been an ideal fit for radar and signal processing applications, which demand powerful and complex computing.

Evaluating determinism, Intel processors have a disadvantaged reputation compared to Power Architecture. Intel processors are known to throttle their clock speed (and thus their performance) based on the processor workload and their thermal environment. This is done automatically to reduce power consumption and protect the hardware from overheating if not adequately cooled. However, for demanding defense applications where predictability is essential, Intel processors can be set to constant clock speeds. Furthermore, choosing boards engineered with advanced cooling techniques and designed to ensure consistent performance is essential. (For more on this subject, read “Understanding Intel Processor Throttling for Defense Applications”.)

ARM processors, on the other hand, deliver many of the benefits that make Power Architecture an ideal fit for DO-254 safety-certifiable applications, but with significant SWaP advantages. Compare, for example, NXP’s QorIQ Layerscape 1043A (LS1043A) ARM processor with its T2080 Power Architecture chip. Relatively, the LS1043A provides approximately the same processor core performance at one third of the power of the T2080 in applications with restrictive SWaP requirements. ARM processors rival Intel’s performance levels, making them equally suitable for radar and signal processing applications – applications where Power Architecture has historically fallen short. What’s more, ARM processors deliver this level of complex computing at a lower performance per watt, without the threat of throttling.

ARM and Power: Cut from the same cloth

When it comes to manufacturing, ARM processors bear another similarity to Power Architecture that make them a prime candidate to fill the void in the DO-254 certifiable hardware space. With IBM introducing its last series of general-purpose Power Architecture processors in 1997, NXP secured its spot as the leading producer in the market. Now with decades of experience and expertise designing chips for a variety of applications, including DO-254 DAL A certifiable hardware, NXP has increased its focus on delivering ARM solutions that meet the demanding requirements of these applications as Power Architecture solutions have, with even higher caliber performance.

Not all cores are created equal

In order to understand ARM’s fit in the DO-254 world, it’s important to note there are three types of ARM architectures:

- Application profile (A-profile): implemented by cores in the Cortex-A series and designed for application use

- Real-time profile (R-profile): implemented by cores in the Cortex-R series and designed for real-time and safety-critical applications

- Microcontroller profile (M-profile): implemented by cores in the Cortex-M series and designed for microcontrollers

For DO-254 safety-certifiable applications, it’s logical to assume that Cortex-R series cores would offer the ideal profile. However, while there’s nothing inherently preventing Cortex-R and -M cores from meeting DO-254 requirements, A-profile architectures in fact provide the best solution for avionics. Cortex-A cores offer the only profile that can run a 64-bit operating system, and provide the level of performance needed to handle the workload and computing requirements of avionics systems.The Cortex-A series offers several 64-bit cores, ranging from Cortex-A35 to Cortex-A76. The sweet spot for mil-aero applications lies in the Cortex-A53, ARM’s first ARMv8-A (the most recently released version of ARM architecture) core designed specifically for providing power-efficient 64-bit processing. While commercially the Cortex-A53 is most commonly known for powering Raspberry Pi 3 computers and Roku media players, ARM Limited describes the Cortex-A53 as a high-efficiency processor ideal for devices requiring high performance in power-constrained technologies, such as smartphones, aerospace applications and automotive infotainment systems.

Not only is this balance between power and performance ideal for managing both the workload and SWaP constraints of airborne systems, the Cortex-A53’s proven service history provides the reliability required for DO-254 certification. Its deterministic processing prevents throttling in challenging mil-aero environments, ensuring consistent levels of performance for safety-critical systems with DAL A requirements, such as flight control computers.

From automotive to aerospace

In recent years, NXP ARM cores have played an integral role in safety-critical automotive systems, such as advanced driver assistance systems (ADAS), in-vehicle networking, powertrain components, and safety applications. Cortex-A53 processing cores, in particular, power NXP’s family of vision processors designed for object detection and recognition, machine learning and sensor fusion applications.

The process of designing electronics in the automotive industry is not unlike that in the aerospace industry. Similar to the Technical Standard Orders (TSOs) that guide certification in avionics, the automotive industry relies on specifications from the International Organization for Standardization (ISO) when designing and testing safety-critical components. In lieu of DALs, the automotive industry classifies risk levels through Automotive Safety Integrity Levels (ASILs). The similarities are so evident that many ASIL descriptions compare its safety levels to DO-254 DALs.

Establishing compliance to the safety requirements outlined in ISO 26262, which prescribes functional safety standards for road vehicles, involves assessing failure modes and testing hardware in a variety of environmental and operational conditions. Interestingly, many areas of the ISO26262 ASIL assessment process align with the hazard analysis and safety assessment requirements for DO-254 certification. This credible experience in safety-critical applications has provided NXP a solid foundation for turning its ARM focus to the skies.

The power of collaboration

On the path to being deemed airworthy, the collection of data artifacts to support DO-254 typically starts at the board level, especially with some hardware vendors now offering to deliver commercially designed boards with data artifact packages for certification. This is where NXP’s experience providing evidence to support certification for its Power Architecture products is again beneficial in its ARM offerings.

Working with NXP from the start of the design process, hardware vendors determine which processor delivers the performance and reliability required for a board’s target applications. Often these applications call for specific system-level protections that require additional logic built into the processor to achieve them, necessitating a level of familiarity with the product only NXP can provide. NXP’s transparency and collaboration with hardware vendors enables such modifications.

Furthermore, a variety of hardware tests required for DO-254 compliance must test functions that originate within the processor itself and are, therefore, difficult for board manufacturers to conduct on a finished chip. NXP provides documentation from the processor’s design, development and manufacturing stages that allows board manufacturers to demonstrate adherence to DO-254 requirements without the complex and time-consuming undertaking of conducting these internal tests themselves.

NXP’s support also allows hardware vendors, who interface directly with system integrators and designers working on certifiable systems, to voice specific customer questions and receive detailed answers from the source in order to eliminate confusion and concerns.

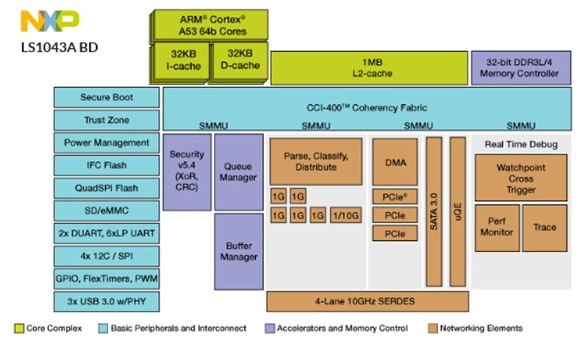

This partnership and collaboration played a key role in Curtiss-Wright’s development of what would become the industry’s first announced DO-254-certifiable ARM SBC, the LS1043A-powered VPX3-1703. Leveraging four Cortex-A53 cores, along with cybersecurity and real-time debug features, the LS1043A has layers of reliability built into its specifications. Delivering the output and processing levels demanded by most DAL A applications, the VPX3- 1703 balances deterministic, high performance with SWaP-friendly power consumption, and a reputable service history with a design for longevity. Having worked closely with NXP throughout the development phase, Curtiss-Wright is able to deliver a full DAL A certification artifacts package with the VPX3-1703.

Conclusion

Reliability and determinism have always been the paramount criteria in the selection process for DO- 254 certifiable avionics. As commercial technology has rapidly evolved, yielding even higher output from increasingly shrinking form factors, performance has emerged as another key factor for evaluation – especially since building with the best technology today can add longevity to a program by (theoretically) extending the time between required upgrades.

With no roadmap on the horizon for Power Architecture devices, ARM is a prime candidate to become the new leading processor architecture powering DO-254 DAL A-certified computing modules. Boasting higher performance capabilities than Power Architecture at lower levels of power consumption, ARM offers an unbeatable power-to-performance ratio to bring substantial outputs to SWaP-constrained environments. In particular, Cortex-A processing cores like the Cortex-A53 provide the ideal performance and power levels for mil-aero applications, and have a reputable service history to support DO-254 certification.

Layerscape 1043A block diagram

Further establishing ARM as a viable alternative to Power Architecture, NXP is devoting the expertise that made it the leading provider of Power Architecture processors toward ARM products. With a breadth of experience designing high quality processors and supporting board manufacturers on the path to DO-254 certification, NXP’s background in helping Power Architecture-based boards meet DAL A standards primes it for the same success with ARM. And, as a key player in safety-critical automotive systems, NXP has already manufactured a variety of ARM cores compliant with stringent safety regulations that provide a solid foundation for DO-254 certification.

Ultimately, the ARM processing architecture seems ready for take-off in the aerospace and defense industry, and it won’t be long before ARM establishes its spot as a key player in DO-254 applications.

Authors

![]() Rick Hearn, Senior Product Manager, Safety Certifiable Solutions, Curtiss-Wright Defense Solutions

Rick Hearn, Senior Product Manager, Safety Certifiable Solutions, Curtiss-Wright Defense Solutions

Rick Hearn is the Product Manager for Safety Certifiable Solutions for Curtiss-Wright Defense Solutions. Rick has over 25 years of experience in design and design management positions in the Telecommunications and Defense industries including 11 years of experience in design management and program management at Curtiss-Wright Defense Solutions.

![]() Mike Slonosky, Senior Product Manager, Power Architecture and Arm SBCs, Curtiss-Wright Defense Solutions

Mike Slonosky, Senior Product Manager, Power Architecture and Arm SBCs, Curtiss-Wright Defense Solutions

Michael Slonosky is the Product Marketing Manager for Power Architecture Single Board Computers in the C4 Solutions group at Curtiss-Wright. He has been with Curtiss-Wright for 13 years after spending over 20 years in the telecom industry. Mike is a graduate of the University Of Manitoba with an Masters of Science in Electrical Engineering.

![]() Geoffrey Waters, Senior Systems Engineer, NXP Semiconductors

Geoffrey Waters, Senior Systems Engineer, NXP Semiconductors

Geoff Waters serves as a Distinguished Member of Technical Staff, covering high-end multi-core products and trusted computing for the Digital Networking group. He leads the Trust Architecture user’s group, and is a regular contributor to the MultiCore for Avionics (MCFA) working group. When Geoff is not working on security acceleration and hardware roots of trust, you’ll find him on the river competing in canoe ultra-marathons and kayak races.

Lisa Sarazin, Marketing Portfolio Manager, Curtiss-Wright Defense Solutions

Lisa Sarazin, Marketing Portfolio Manager, Curtiss-Wright Defense Solutions

Lisa Sarazin is the Marketing Portfolio Manager for the C4S division of Curtiss-Wright Defense Solutions. Lisa has previously held roles in Product Marketing and Content Strategy in the telecommunications and software industries.

1 Note: CPU DMIPS for Intel includes processor only and excludes the PCH

2 https://community.ARM.com/processors/b/blog/posts/inside-the-numbers-100-billion-ARM-based-chips-1345571105

3 Apple is a trademark of Apple Inc., registered in the U.S. and other countries